출처: https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=golsm21&logNo=120141464685

SPI

1). 개요

(1). SPI는 일반적으로 외부 디바이스와 4핀으로 연결됨.

①. MISO

– Master In / Slave Out data.

– Master 모드에서는 입력, Slave 모드에서는 출력 신호로 사용됨.

②. MOSI

Master Out/ Slave In data.

Master 모드에서는 출력, Slave 모드에서는 입력 신호로 사용됨.

③. SCK

디바이스에서 사용될 클럭을 공급함.

데이터 송/수신이 있는 경우에만 동작함.

④. NSS

Slave Select. 혹은 Chip select로 명명됨.

디바이스를 활성화 하는 신호로 쓰임.

2). NSS pin management

(1). Software NSS Mode

①. SPI_CR1 레지스터에 SSM비트를 설정하면 사용 가능.

②. 어플리케이션에서 자유롭게 제어 할 수 있음.

(2). Hardware NSS mode

①. NSS output is enabled

STM32F10xxx가 마스터로 동작하고 있을 때 SPI_CR2레지스터의 SSOE 비트 설정으로 Enable 됨.

NSS 핀이 low 신호로 동작 할 때, Master NSS에 연결된 모든 NSS핀이 low 레벨 신호 일 때에 사용됨.

②. NSS output is disabled

Multmaster 인 경우 사용.

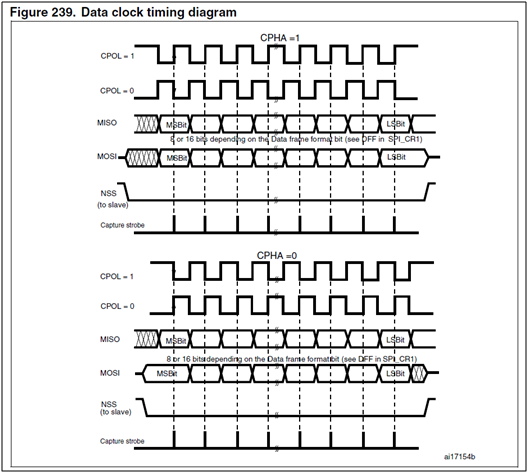

(3). Clock Phase and clock polarity

①. Clock Phase, Clock Polarity를 이용해서 데이터를 어느 순간에 읽을 것인지를 결정 할 수 있으며 이들 조합은 총 4가지의 경우가 존재 한다.

②. SPOL/SPHA를 변경하려면 SPE비트를 리셋 해줘야 한다.

③. 자세한 차이점은 아래 그림을 참조 바람.

(4). SPI master mode 환경 설정

①. SPI_CR1 레지스터에 BR필드를 이용하여 전송 클럭 속도를 설정한다.

②. CPOL, CPHA 비트를 이용하여 데이터 전송모드를 설정한다.

③. DFF 비트를 이용하여 데이터 프레임 사이즈를 설정한다.

④. LSBFIRST 비트를 이용하여 MSB, LSB를 설정한다.

⑤. SSM, SSI 비트를 이용하여 NSS 핀 상태(Hardware or Software)를 설정한다.

⑥. MSTR, SPE 비트를 이용하여 디바이스를 활성화 시킨다.

(5). Transmit sequence

①. Tx buffer에 전송할 바이트를 쓰면 해당 바이트는 실시간으로 전송된다.

②. 데이터 바이트는 SPI_CR1 레지스터의 LSBFIRST 비트에 따라 LSB 혹은 MSB가 첫 번째 비트가 전송되는 동안 shift register에 병렬로 로드된다.

③. TXE 플래그는 Tx 버퍼에서 Shift register로 전송이 완료 되면 설정되고 SPI_CR2 레지스터에 TXEIE 비트 설정 여부에 따라 인터럽트가 발생된다.

(6). Receive sequence

①. Shift Register에 데이터가 Rx Buffer로 전송이 완료 되어졌을 때 RXNE 플래그가 설정되고 수신이 완료 된다.

②. SPI_CR2 레지스터에 RXNEIE 비트 설정 여부에 따라 인터럽트가 발생된다.

③. Shift Register에서 수신된 데이터의 복사본은 Rx_buffer로 옮겨지고 마지막 클럭 엣지에서 RXNE 비트가 설정된다. 이때 SPI_DR 레지스터를 읽으면 SPI는 이 버퍼의 값을 리턴한다.

④. SPI_DR 레지스터를 읽으면 RXNE비트는 클리어 된다.

⑤. 전송되기 위한 다음데이터가 Tx Buffer에 쓰이면 연속된 데이터는 유지된다.

⑥. Tx buffer에 쓰기 전에 TXE 플래그는 1이 되어 있어야 한다.

(7). Data transmission and reception procedures

①. Rx and Tx buffers

데이터 수신 되어지면 SPI 내부에 Rx Buffer에 저장되어 진다.

데이터를 전송할 때는 전송이 시작되기 전에 내부 Tx buffer에 저장된다.

SPI_DR 레지스터는 읽으면 Rx buffer의 값이 전달되고 SPI_DR레지스터에 쓰면 Tx Buffer로 값이 전송된다.

②. In full-duplex

SPI_DR 레지스터에 값을 쓰면 통신 신호가 발생된다.

Tx buffer로부터 paralled하게 로드 되고 8-bit shift register로 그리고 MOSI핀을 통해 디바이스에 신호가 전달된다.

동시에 MISO핀을 통해 수신되어지는 데이터는 8-bit shift register를 통해 Rx buffer로 전달이 되고 SPI_DR 레지스터를 읽으면 Rx_buffer의 내용일 읽어지게 된다.

(8). Handling data transmission and reception

①. TXE Flag

TXE flag는 Tx buffer에서 Shift Register로 데이터가 전송되면 ‘1’로 설정된다.

내부 Tx buffer는 다음 데이터가 Load될 준비가 되었다는 것을 나타낸다

SPI_CR2 레지스터에 TXEIE비트가 설정되어 있다면 해당 인터럽트가 발생될 것이다.

SPI_DR레지스터에 데이터가 써지면 TXE 비트는 ‘0’으로 클리어 된다.

②. 주의

소프트웨어는 Tx buffer에 쓰기전에 TXE 플래그가 1로 셋팅되어 있는 것을 반드시 확인 한다.

③. RXNE Flag

데이터는 Shift Register로부터 Rx buffer로 전송되며 RXNE Flag는 마지막 클럭 엣지에 설정된다.

이것은 SPI_DR레지스터로부터 읽을 준비가 되어 있음을 나타내는 신호이다.

SPI_CR2레지스터의 RXNEIE비트가 설정되어 있으면 해당 인터럽트가 발생한다.

SPI_DR 레지스터를 읽으면 RXEN 비트는 클리어 된다.

④. BSY flag

BSY flag는 마지막 바이트 전송이 완료 될 때 까지 BSY 상태를 확인 수 있다